#3/ Priority

11/27/01

Attorney's Docket No.: 12732-068001 / US5147/5193

# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

Applicant: Hideto Ohnuma et al.

Art Unit : Unknown

Serial No.: Unassigned

Examiner: Unknown

Filed

: August 10, 2001

Title : METHOD OF

: METHOD OF MANUFACTURING A SEMICONDUCTOR DEVICE

Commissioner for Patents Washington, D.C. 20231

# TRANSMITTAL OF PRIORITY DOCUMENT UNDER 35 USC §119

Applicants hereby confirms their claim of priority under 35 USC §119 from the following applications:

Japan Application No. 2000-244860 filed August 11, 2000 Japan Application No. 2000-267851 filed September 4, 2000

A certified copy of each application from which priority is claimed is submitted herewith. Please apply any charges or credits to Deposit Account No. 06-1050.

Respectfully submitted,

Date: August 10, 2001

John F. Hayden Reg. No. 37,640

Fish & Richardson P.C. 601 Thirteenth Street, NW Washington, DC 20005

Telephone: (202) 783-5070 Facsimile: (202) 783-2331

40065178.doc

# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日

Date of Application:

2000年 8月11日

出願番号

Application Number:

特願2000-244860

出 願 人 Applicant(s):

株式会社半導体エネルギー研究所

2001年 6月12日

特 許 庁 長 官 Commissioner, Japan Patent Office

### 特2000-244860

【書類名】

特許願

【整理番号】

P005147

【提出日】

平成12年 8月11日

【あて先】

特許庁長官 及川 耕造 殿

【発明者】

【住所又は居所】

神奈川県厚木市長谷398番地 株式会社半導体エネル

ギー研究所内

【氏名】

大沼 英人

【特許出願人】

【識別番号】

000153878

【氏名又は名称】 株式会社半導体エネルギー研究所

【代表者】

山崎 舜平

【手数料の表示】

【予納台帳番号】

002543

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【プルーフの要否】

要

### 【書類名】明細書

【発明の名称】 半導体装置の製造方法

【特許請求の範囲】

### 【請求項1】

回折格子パターンを有するフォトマスクまたはレチクルを使用してゲート電極形成用のレジストパターンを形成する第1の工程と、前記レジストパターンをマスクとしてドライエッチングを行い、端部に膜厚の薄い領域を有するゲート電極を形成する第2の工程と、一導電型の不純物をイオン注入して、前記ゲート電極の外側領域に対応する半導体層または半導体基板に第1の不純物領域を形成する第3の工程と、前記レジストパターンを除去する第4の工程と、前記一導電型の不純物をイオン注入して、前記ゲート電極の外側領域に対応する半導体層または半導体基板に第2の不純物領域と前記膜厚の薄い領域に対応する半導体層または半導体基板に第2の不純物領域を形成する第5の工程とを有することを特徴とする半導体基置の製造方法。

### 【請求項2】

半透膜を有するフォトマスクまたはレチクルを使用してゲート電極形成用のレジストパターンを形成する第1の工程と、前記レジストパターンをマスクとしてドライエッチングを行い、端部に膜厚の薄い領域を有するゲート電極を形成する第2の工程と、一導電型の不純物をイオン注入して、前記ゲート電極の外側領域に対応する半導体層または半導体基板に第1の不純物領域を形成する第3の工程と、前記レジストパターンを除去する第4の工程と、前記一導電型の不純物をイオン注入して、前記ゲート電極の外側領域に対応する半導体層または半導体基板に第2の不純物領域と前記膜厚の薄い領域に対応する半導体層または半導体基板に第2の不純物領域を形成する第5の工程とを有することを特徴とする半導体装置の製造方法。

#### 【請求項3】

請求項1に於いて、前記回折格子パターンは複数のスリット部で構成されている ことを特徴とする半導体装置の製造方法。

#### 【請求項4】

請求項1または2に於いて、前記第2の不純物領域はソース及びドレイン領域となる高濃度不純物領域であり、前記第3の不純物領域は低濃度不純物領域であることを特徴とする半導体装置の製造方法。

#### 【請求項5】

請求項1または2に於いて、前記半導体装置は多結晶薄膜トランジスタで構成されていることを特徴とする半導体装置の製造方法。

### 【請求項6】

請求項1または2に於いて、前記半導体装置はMOS型トランジスタで構成されている

ことを特徴とする半導体装置の製造方法。

### 【発明の詳細な説明】

[0001]

#### 【発明の属する技術分野】

本発明は薄膜トランジスタ(以下、TFTと略記)及びMOSトランジスタで構成された回路を有する半導体装置の製造法に関するものである。半導体装置としては、例えばTFTで構成された液晶ディスプレイ及びEL(エレクトロルミネッセンス)ディスプレイ等の電気光学装置があり、MOSトランジスタで構成されたLSIがある。

[0002]

#### 【従来の技術】

近年、TFTを利用したアクティブマトリクス型の液晶ディスプレイ技術が注目されている。アクティブマトリクス表示はパッシブマトリクス表示に比べ、応答速度、視野角、コントラストの点で有利な為、現在のノートパソコン、液晶テレビ等の主流になっている。

[0003]

TFTは、非晶質シリコンまたは多結晶シリコンをチャネル層とするものが一般的である。特に低温プロセス(一般に600℃以下)のみで製造される多結晶シリコンTFTは、低価格化、大面積化と同時に、電子または正孔が大きな電界移動度を有する為、液晶ディスプレイに用いた場合、画素用トランジスタだけで

なく周辺回路であるドライバーの一体化が達成できる特徴があり、各液晶ディス プレイメーカーで開発が進められてきた。

### [0004]

しかし、多結晶シリコンTFTの場合、連続駆動させると移動度やオン電流( TFTがオン状態の場合に流れる電流)の低下及びオフ電流(TFTがオフ状態 の場合に流れる電流)の増加等の信頼性上の劣化現象が観測されることがある。 この現象はホットキャリア現象と呼ばれており、ドレイン近傍の高電界により発 生したホットキャリアの仕業であることが知られている。

### [0005]

ところで、このホットキャリア現象は、最初にMOSトランジスタに於いて発見された現象である。この為、ホットキャリア対策として、これまで様々な基礎検討が行われてきており、設計ルール1.5μm以下のMOSトランジスタでは、ドレイン近傍の高電界によるホットキャリア現象の対策として、LDD (Lightly Doped Drain) 構造が採用されている。LDD構造では、ゲート側壁のサイドウォールを利用してドレイン端部に低濃度不純物領域(nー領域)を設け、ドレイン接合の不純物濃度に傾斜を持たせることによりドレイン近傍の電界集中を緩和している。

### [0006]

しかし、LDD構造の場合、シングルドレイン構造に比べ、ドレイン耐圧はかなり向上するが、低濃度不純物領域(n-領域)の抵抗が大きい為、ドレイン電流が減少するという難点が有る。また、サイドウォールの真下に高電界領域が存在し、そこで衝突電離が最大になり、ホットエレクトロンがサイドウォールに注入される為、低濃度不純物領域(n-領域)が空乏化し、更に抵抗が増加するLDD特有の劣化モードが問題になっている。チャネル長の縮小に伴い、以上の問題が顕在化してきた為、0.5μm以下のMOSトランジスタでは、この問題を克服する構造として、ゲート電極の端部にオーバーラップして低濃度不純物領域(n-領域)を形成するGOLD(Gate-drain Overlapped LDD)構造が考案され採用されている。

[0007]

多結晶シリコンTFTに於いても、MOSトランジスタと同様にドレイン近傍の高電界を緩和する目的で、LDD構造及びGOLD構造の採用が検討されている。LDD構造の場合は、ゲート絶縁膜の下層膜である多結晶シリコン層に高濃度不純物領域(n+領域)であるソース及びドレイン領域とその内側に低濃度不純物領域(n-領域)を形成しており、オフ電流値を抑える効果は高いが、ドレイン近傍の電界緩和によるホットキャリア対策効果は小さいという特徴がある。一方、GOLD構造の場合は、LDD構造の低濃度不純物領域(n-領域)がゲート電極端部とオーバーラップする様に形成されており、LDD構造に比べホットキャリア対策効果は大きいが、オフ電流値が大きくなるという点が難点である

[0008]

### 【発明が解決しようとする課題】

多結晶シリコンTFT及びMOSトランジスタに於けるLDD構造とGOLD構造のソースドレイン領域となる高濃度不純物領域(n+領域)及びその内側の低濃度不純物領域(n-領域)の形成は、従来、ゲート電極をマスクにセルフアラインで形成しており、フォトリソグラフィ工程の増加を抑制できる利点があるが、ゲート電極が2層構造となる為、成膜工程とエッチング工程が複雑になるという課題がある。

#### [0009]

また、半導体装置には様々な回路が内包されており、回路によってはホットキャリア対策効果に優れたGOLD構造が適している場合もあれば、オフ電流値の小さいLDD構造が適している場合もあり、場合によっては、シングルドレイン構造が適している場合もある。LDD構造及びGOLD構造の形成は、ドライエッチング等のプロセスのみで形成する為、半導体装置内のトランジスタ構造が全て同一構造となり、回路毎にシングルドレイン構造とLDD構造及びGOLD構造を別々に形成することができない点が課題である。

#### [0010]

また、GOLD構造に於いては、低濃度不純物領域(n-領域)の長さが、基本的にサイドエッチング等のエッチングにより形成される第1層ゲート電極膜の

みが存在する領域で決まる為、低濃度不純物領域(n-領域)の長さに制約が生じ、またはその長さを十分に確保できない等の課題が有る。

本発明は、上記課題を解決することのできる半導体装置の製造法を提供することを目的とする。

### [0011]

### 【課題を解決する為の手段】

フォトリソグラフィ工程で使用されるゲート電極形成用フォトマスクまたはレチクルに於いて、ゲート電極形成用マスクパターンの片側または両側の端部に露光光の光強度を低減する機能を有する補助パターンを設置する。前記補助パターンでの露光光の光強度の低減機能を有する具体的パターンとしては、解像限界以下のライン/スペースから成るスリット部を有する回折格子パターンと露光光の透過率を低減する半透膜が考えられる。回折格子パターンの場合は、スリット(スペース)部のピッチとスリット幅を調整することにより、透過光の光強度を調整することができる。一方の半透膜の場合は、半透膜の透過率を調整することにより、透過光の光強度を調整することができる。

### [0012]

尚、このフォトリソグラフィ工程で使用されるレジストはネガ型レジストが適 用困難である為、当該ゲート電極形成用フォトマスクまたはレチクルのパターン 構成は、ポジ型レジストを前提にしている。

### [0013]

前記ゲート電極形成用フォトマスクまたはレチクルを用いて露光した場合、ゲート電極形成用マスクパターンの主パターンの領域は、遮光部である為に光強度はゼロであり、前記補助パターンの更に外側の領域は透光部である為、光強度は100%である。一方、前記補助パターン領域では、光強度が10~70%の範囲で調整されている。前記ゲート電極形成用フォトマスクまたはレチクルをフォトリソグラフィ工程に適用することにより、レジストパターンの片側または両側の端部の現像後レジスト膜厚が、通常のレジスト膜厚に比べ10~60%の範囲で薄く形成される。従って、レジストパターンの両側の端部が薄く形成された場合には、凸形状のレジストパターンが形成される。

#### [0014]

ところで、ステッパ等の縮小投影露光装置を使用する単波長露光の場合、露光 光の位相が或る程度揃っているパーシャルコヒーレント光である為、補助パター ンとして半透膜を適用すると、半透膜がハーフトーン型位相シフタとして作用す ることが考えられる。この場合は、隣接する露光光との間の位相が180°程度 に反転しない様に半透膜の膜厚の調整に注意が必要で、できれば360°程度に なる様に調整する。従って、縮小投影露光装置に適用されるレチクルの場合には 、補助パターンとして、半透膜を適用する上に於いて、位相シフト量と透過率の 両方を考慮して、半透膜の膜厚を調整する。

### [0015]

また、本発明のフォトリソグラフィ工程に於いては、ポジ型レジストのみを前提にしていることは既に述べたが、ここではその理由について説明する。ネガ型レジストの場合はポジ型レジストと逆に、ゲート電極形成用フォトマスクまたはレチクルの主パターン領域が透光部で、補助パターンの外側の領域が遮光部であり、補助パターン領域が光強度調整部(光強度を10~70%程度の範囲で調整)のパターン構成となっている。前記パターン構成を有するフォトマスクまたはレチクルを用いて、ネガ型レジストを露光した場合、補助パターン領域にはレジストパターン形成に必要十分な露光エネルギーが照射されない為、レジスト膜の上層部のみ露光された状態となり、下層部は未露光または露光不足の状態となっている。この状態のネガ型レジストを現像した場合、当該領域のレジスト膜の上層部は現像液に不溶であるが、下層部が現像液に可溶である為、レジスト膜の下層部のみをレジスト残膜とする良好なパターン形成ができない。

### [0016]

上記理由の為、本発明のフォトリソグラフィ工程に於いては、ネガ型レジスト は適用困難であり、ポジ型レジストのみの適用となっている。

#### [0017]

上記フォトリソグラフィ工程により、片側または両側の端部のレジスト膜厚が 薄くなったレジストパターンを形成した後、ドライエッチング処理を行う。ドラ イエッチング工程に於いて、レジストパターン端部のレジスト膜厚の薄く形成さ れた領域は、ゲート電極膜とレジスト膜との選択比の問題で、徐々にエッチングされ、ドライエッチングの途中で下地のゲート電極膜が露出し、この段階から当該領域のゲート電極膜のエッチングが進行し、ゲート電極膜の残膜厚が初期膜厚の5~30%程度の所定膜厚になる様にエッチングされる。この様にして、ゲート電極の片側または両側の端部が薄くなった領域を有するゲート電極構造が形成される。

#### [0018]

次に前記ゲート電極をマスクにn型不純物をイオン注入することにより、ゲート電極の外側に対応する下層領域にソース及びドレイン領域となる高濃度不純物領域(n+領域)が形成され、当該ゲート電極の片側または両側のゲート電極膜の薄くなった領域に対応する下層領域に低濃度不純物領域(n-領域)が形成される。この際、ゲート電極の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、高濃度不純物領域(n+領域)と低濃度不純物領域(n-領域)を同時に形成することができる。尚、ゲート電極を形成した際のドライエッチングマスクであるレジストパターンは、イオン注入工程の前後のどちらで除去しても良い。

#### [0019]

以上はGOLD構造トランジスタの形成法について記載したものであるが、半導体装置には様々な回路が内包されており、回路によってはホットキャリア対策効果に優れたGOLD構造トランジスタが適している場合もあれば、オフ電流値の小さいLDD構造トランジスタが適している場合もある。また場合によっては、シングルドレイン構造トランジスタが適している場合もある。よって、回路毎にGOLD構造とLDD構造及びシングルドレイン構造トランジスタを別々に形成する方法について、以下に記載する。

#### [0020]

GOLD構造とLDD構造トランジスタを回路毎に別々に形成する方法については、イオン注入工程からのプロセス変更で対応できる。ドライエッチング工程が終了した後、第1のイオン注入工程を行うことにより、前記ゲート電極の外側に対応する下層領域に低濃度不純物領域(nー領域)が形成される。次に、ゲー

ト電極を形成した際のドライエッチングマスクであるレジストパターンを除去する。尚、前記レジストパターンの除去は、第1のイオン注入工程の前に行っても良い。次にLDD構造形成領域に於いては、前記ゲート電極を被覆する様に、新たにレジストパターンを形成する。次に第2のイオン注入を行うことにより、ソース及びドレイン領域となる高濃度不純物領域(n+領域)を形成する。

### [0021]

この際、LDD構造形成領域に於いては、ゲート電極を被覆しているレジストパターンをマスクにイオン注入することにより、レジストパターンから露出した領域に対応する下層領域にソース及びドレイン領域となる高濃度不純物領域(n+領域)が形成される。ゲート電極の外側で且つレジストパターンの内側の領域に対応する下層領域には、既に第1のイオン注入工程により低濃度不純物領域(n-領域)が形成されており、今回の高濃度不純物領域(n+領域)の形成により、LDD構造トランジスタが形成される。

# [0022]

一方、GOLD構造形成領域に於いては、ゲート電極をマスクにイオン注入が行われることにより、ゲート電極から露出した領域に対応する下層領域にソース及びドレイン領域となる高濃度不純物領域(n+領域)が形成され、同時に当該ゲート電極の片側または両側のゲート電極膜の薄くなった領域に対応する下層領域に低濃度不純物領域(n-領域)が形成される。GOLD構造トランジスタは、ゲート電極での端部の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、高濃度不純物領域(n+領域)と低濃度不純物領域(n-領域)を同時に形成することで実現できる。

### [0023]

尚、既にゲート電極から露出した領域には、第1のイオン注入工程により低濃度不純物が注入されており、その上から第2のイオン注入工程である高濃度不純物が注入されることになるが、ソース及びドレイン領域となる高濃度不純物領域(n+領域)の形成には特に支障は起こらない。この後に、LDD構造形成領域に形成された前記レジストパターンを除去する。

### [0024]

次に、シングルドレイン構造トランジスタの形成法について、以下に記載する。シングルドレイン構造トランジスタの形成は簡単で、ゲート電極形成用フォトマスクまたはレチクルに於ける光強度低減機能を有する補助パターンを設置しない場合に、シングルドレイン構造トランジスタの形成が可能となる。光強度低減機能を有する補助パターンがない場合は、ゲート電極形成用レジストパターンとゲート電極が各々矩形形状となる為、上記の第1のイオン注入工程と第2のイオン注入工程で注入される低濃度不純物領域(nー領域)と高濃度不純物領域(nー領域)が当該ゲート電極の外側に対応する下層領域で重なり、シングルドレイン構造トランジスタが形成される。

### [0025]

既に記載したGOLD構造とLDD構造トランジスタの形成法と上記のシングルドレイン構造トランジスタの形成法を合わせることにより、回路毎にGOLD構造とLDD構造とシングルドレイン構造トランジスタを別々に形成することが可能となる。

#### [0026]

本発明は、マスクパターンに光強度低減機能を有する補助パターンを設置した ゲート電極形成用フォトマスクまたはレチクルをフォトリソグラフィ工程に適用 することにより、エッチング及びイオン注入工程を通し、簡単にGOLD構造ト ランジスタから成る半導体装置を製造可能とするものである。

#### [0027]

また、GOLD構造トランジスタに於いては、マスクパターンに設置する光強 度低減機能を有する補助パターンの寸法は任意の長さに設定可能である為、低濃 度不純物領域(n-領域)のチャネル方向寸法も任意の長さに形成でき、GOL D構造トランジスタの性能向上を可能とするものである。

#### [0028]

また、前記GOLD構造トランジスタから成る半導体装置の製造に於いて、イオン注入工程を2回に分け、低濃度不純物用の第1のイオン注入工程を処理し、次にLDD構造形成領域のみにゲート電極を被覆する様にレジストパターンを形成した後に、高濃度不純物用の第2のイオン注入を処理する様にプロセスの変更

を行うことにより、LDD構造とGOLD構造トランジスタを回路毎に別々に形成可能とするものである。

[0029]

また、前記ゲート電極形成用フォトマスクまたはレチクルに於いて、任意のマスクパターンに光強度低減機能を有する補助パターンを設置することにより、半導体装置の回路パターン毎にシングルドレイン構造とGOLD構造トランジスタを別々に形成することを可能とするものである。

[0030]

### 【発明の実施の形態】

#### (実施形態1)

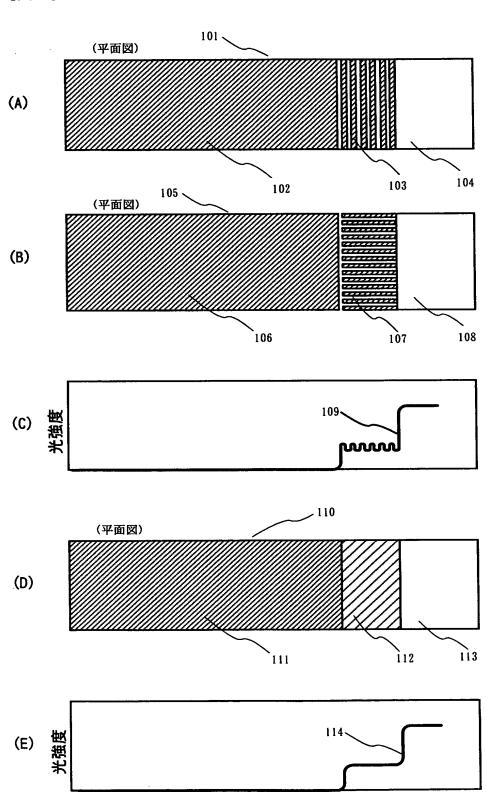

回折格子パターンまたは半透膜から成る光強度低減機能を有するゲート電極形成用フォトマスクまたはレチクルを利用したフォトリソグラフィ工程をGOLD構造多結晶シリコンTFTの形成に適用した場合について、図1~図2に基づき記載する。

最初に回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルの構成について、図1を用いて説明する。

### [0031]

ゲート電極形成用フォトマスクまたはレチクルに於けるマスクパターンの片側または両側の端部に光強度低減機能を有する補助パターンを設置する。この補助パターンの具体例として、図1 (A)と図1 (B)に解像限界以下のライン/スペースから成るスリット部を有する回折格子パターンの例を示す。尚、このフォトリソグラフィ工程で使用されるレジストはネガ型レジストが適用困難である為、当該ゲート電極形成用フォトマスクまたはレチクル101,105のパターン構成は、ポジ型レジストを前提にしている。よって、ゲート電極形成用マスクパターンの主パターンの領域が遮光部102,106で、光強度低減機能を有する補助パターンの領域がスリット部103,107で、補助パターンの外側の領域が透光部104,108のパターン構成となっている。前記スリット部のスリットの方向は、スリット部103の様に主パターン(遮光部102)の方向と平行

でも、スリット部107の様に主パターン(遮光部106)の方向と垂直でも構 わない(図1(A)と図1(B))。

#### [0032]

前記ゲート電極形成用フォトマスクまたはレチクル101,105に露光光を 照射した場合、遮光部102,106の光強度はゼロであり、透光部104,1 08の光強度は100%である。一方、解像限界以下のライン/スペースから成 る回折格子パターンのスリット部103,107で構成される光強度低減機能を 有する補助パターンの光強度は、10~70%の範囲で調整可能となっており、 その代表的光強度分布の例を光強度分布109に示す。回折格子パターンに於け る前記スリット部103,107の光強度の調整は、スリット部103,107 のピッチ及びスリット幅の調整により実現している(図1(C))。

#### [0033]

次に補助パターンの具体例として、図1 (D) に露光光の光強度を低減する機能を有する半透膜の例を示す。ゲート電極形成用フォトマスクまたはレチクル110に於けるゲート電極形成用マスクパターンの主パターンの領域が遮光部11で、光強度低減機能を有する補助パターンの領域が半透膜から成る半透光部112で、その外側の領域が透光部113である(図1(D))。

#### [0034]

前記ゲート電極形成用フォトマスクまたはレチクル110に露光光を照射した場合、遮光部111及び透光部113の光強度は各々ゼロと100%であり、半透膜から成る半透光部112で構成される補助パターン領域の光強度は、10~70%の範囲で調整可能となっており、その代表的光強度分布の例を光強度分布114に示す(図1-E)。

### [0035]

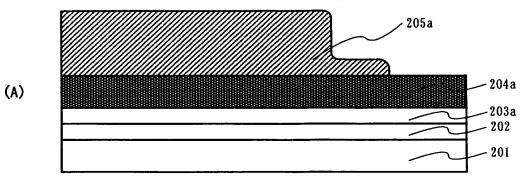

次に回折格子パターンまたは半透膜から成る光強度低減機能を有するゲート電極形成用フォトマスクまたはレチクル101,105,110を利用したGOL D構造多結晶シリコンTFTの形成法について、図2を用いて説明する。

#### [0036]

回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターン

を設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105, 110をフォトリソグラフィ工程に適用することにより、レジストパターンの片 側または両側の端部に於いて、現像後レジスト膜厚が通常に比べ、10~60% の範囲で薄くなった現像後レジストパターン205aを形成する(図2(A))

### [0037]

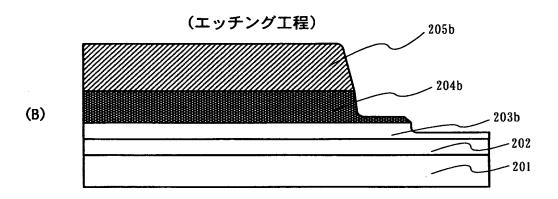

次に、前記現像後レジストパターン205aをマスクに、ドライエッチング処理を行う。ドライエッチング工程に於いて、前記現像後レジストパターン205aから露出しているゲート電極膜204aは、完全にエッチングされ、更に下層側に存在する酸化窒化シリコン膜から成るゲート絶縁膜203aが若干オーバーエッチングされるまでドライエッチング処理を行う。一方、前記現像後レジストパターン205aの片側または両側の端部のレジスト膜厚が薄くなった領域は、ゲート電極膜204aとの選択比の問題で、レジスト膜が徐々にエッチングされ、ドライエッチングの途中で当該領域のレジスト膜が消失し、その下側のゲート電極膜204aが露出し、この段階から当該領域のゲート電極膜204aのエッチングが進行し、その残膜厚が初期膜厚の5~30%の所定膜厚になる様にエッチングされる。

#### [0038]

ここで、ドライエッチング工程に於けるレジストパターンの形状は、片側または両側の端部のレジスト膜厚が薄くなった領域を有する現像後レジストパターン205aから、最終的にはドライエッチング後レジストパターン205bの形状に変化している。ドライエッチングにより、ゲート電極膜の片側または両側の端部が薄くなった領域を有するゲート電極204bが形成され、前記ゲート電極204bから露出した領域に存在する下層膜である酸化窒化シリコン膜から成るゲート絶縁膜203bは、オーバーエッチングにより薄くなった形状になっている(図2(B))。

#### [0039]

次に当該ゲート電極204bをマスクとして、ソース及びドレイン領域にn型 不純物の高濃度イオン注入を行う。片側または両側の端部が薄くなった領域を有 するゲート電極204bから露出した領域に対応する多結晶シリコン膜202に、ソース及びドレイン領域となる高濃度不純物領域(n+領域)206が形成される。更に、当該ゲート電極204bの端部の膜厚が薄い領域に対応する多結晶シリコン膜202に低濃度不純物領域(n-領域)207が形成される。この際、前記高濃度不純物領域(n+領域)206と前記低濃度不純物領域(nー領域)207は、ゲート電極の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、高濃度不純物領域(n+領域)206と低濃度不純物領域(nー領域)207を同時に形成することができる。尚、ドライエッチング後レジストパターン205bは、イオン注入工程の前または後の工程のどちらで除去しても良い(図2(C))。

### [0040]

尚、ここではGOLD構造多結晶シリコンTFTの形成法について記載したが、光強度低減機能を有する補助パターンを設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105,110は、シリコン基板等の半導体基板を使用するGOLD構造MOS型トランジスタの形成にも、勿論適用可能である。この場合は、ソース及びドレイン領域となる高濃度不純物領域(n+領域)とゲート電極とオーバーラップしている低濃度不純物領域(nー領域)は、各々シリコン基板等の半導体基板に形成される。

#### [0041]

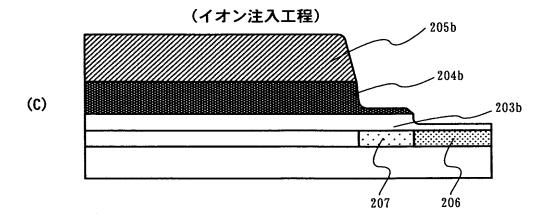

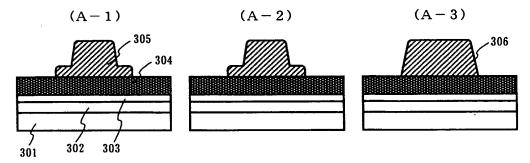

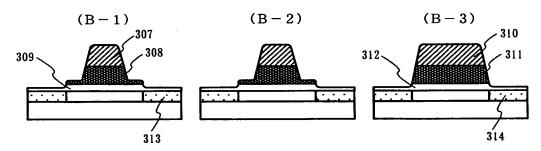

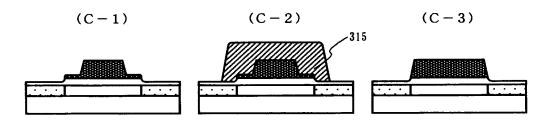

### (実施形態2)

液晶ディスプレイ等の半導体装置には様々な回路が内包されており、回路によってはホットキャリア対策効果に優れたGOLD構造が適している場合もあれば、オフ電流値の小さいLDD構造が適している場合もあり、場合によっては、シングルドレイン構造が適している場合もある。従って、回路毎にGOLD構造及びLDD構造とシングルドレイン構造の多結晶シリコンTFTを別々に形成する必要がある。実施形態2に於いては、回路毎にGOLD構造とLDD構造及びシングルドレイン構造の多結晶シリコンTFTを別々に形成する方法について、図3に基づき記載する。尚、前記ゲート電極形成用フォトマスクまたはレチクル101,105,110(図1(A),(B),(D))の構成については、既に

実施形態1に記載している為、ここでは割愛する。

[0042]

ここで使用する基板構造についてであるが、石英ガラス等から成るガラス基板301上に所定膜厚の多結晶シリコン膜302と酸化窒化シリコン膜から成る所定膜厚のゲート絶縁膜303と所定膜厚のゲート電極膜304が各々積層されている構造の基板を使用する。前記構造の基板上に、回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクル101,105,110(図1(A),(B),(D))を適用したフォトリソグラフィ工程を行い、ゲート電極形成用の現像後レジストパターン305,306を形成する。

[0043]

尚、GOLD構造形成領域401とLDD構造形成領域402に於いては、マスクパターンに回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンが設置されている為、両側の端部のレジスト膜厚が通常に比べ、10~60%の範囲で薄くなった現像後レジストパターン305が形成される。一方、シングルドレイン構造形成領域403に於いては、マスクパターンに前記補助パターンがない為、通常の矩形形状の現像後レジストパターン306が形成される(図3(A))。

[0044]

次に、前記現像後レジストパターン305,306をマスクにドライエッチング処理を行う。ドライエッチング工程に於いて、GOLD構造形成領域401とLDD構造形成領域402に於ける現像後レジストパターン305から露出しているゲート電極膜304、並びにシングルドレイン構造形成領域403に於ける現像後レジストパターン306から露出しているゲート電極膜304は、各々完全にエッチングされ、更に下層側に存在する酸化窒化シリコン膜から成るゲート絶縁膜303が若干オーバーエッチングされるまでドライエッチング処理を行う

[0045]

GOLD構造形成領域401とLDD構造形成領域402に於ける現像後レジ

ストパターン305の両側端部のレジスト膜厚が薄くなった領域は、ゲート電極膜304との選択比の問題で、レジスト膜が徐々にエッチングされ、ドライエッチングの途中で当該領域のレジスト膜が消失し、その下側のゲート電極膜304が露出し、この段階から当該領域のゲート電極膜304のエッチングが進行し、その残膜厚が初期膜厚の5~30%の所定膜厚になる様にエッチングされる。ここで、ドライエッチング工程に於けるレジストパターンの形状は、現像後レジストパターン305から、最終的にドライエッチング後レジストパターン307の形状に変化している。ドライエッチングにより、パターン両側の端部が薄くなった領域を有するゲート電極308が形成され、前記ゲート電極308から露出した領域に存在する下層膜である酸化窒化シリコン膜から成るゲート絶縁膜309は、オーバーエッチングにより薄くなった形状になっている。

### [0046]

一方、シングルドレイン構造形成領域403に於ける現像後レジストパターン306をマスクにドライエッチングした場合、レジスト膜から露出した領域に存在する下層膜であるゲート電極膜304は完全にエッチングされ、ゲート電極311が形成される。また、更に下層膜である酸化窒化シリコン膜から成るゲート絶縁膜303が若干オーバーエッチングされるまでドライエッチング処理が行われることにより、オーバーエッチングにより薄くなった形状のゲート絶縁膜312が得られる(図3(B))。

#### [0047]

次に、ドライエッチングにより形成されたゲート電極308,311をマスクに第1のイオン注入処理であるn型不純物の低濃度イオン注入を行い、ゲート電極308,311から露出した領域に対応する多結晶シリコン膜302に低濃度不純物領域(n-領域)313,314を形成する(図3)6)。

#### [0048]

次に、ドライエッチングのマスクとなった不要なドライエッチング後レジストパターン307,310をレジスト除去する。そして、LDD構造形成領域402に於いて、ゲート電極308を覆う様に、レジストパターン315を新規に形成する(図3(C))。

[0049]

次に、第2のイオン注入処理であるn型不純物の高濃度イオン注入を行う。この際、GOLD構造形成領域401に於いては、ゲート電極308をマスクにイオン注入が行われることにより、ゲート電極308から露出した領域に対応する多結晶シリコン膜302にソース及びドレイン領域となる高濃度不純物領域(n+領域)316が形成され、同時に当該ゲート電極308の両側に存在するゲート電極膜の薄くなった領域に対応する多結晶シリコン膜302に低濃度不純物領域(n-領域)317が形成される。GOLD構造多結晶シリコンTFTは、ゲート電極308に於ける端部の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、高濃度不純物領域(n+領域)316と低濃度不純物領域(n-領域)317を同時に形成することで実現できる。

[0050]

尚、既にゲート電極308から露出した領域には、第1のイオン注入処理により低濃度不純物領域(n-領域)313が形成されており、その上から第2のイオン注入処理である高濃度不純物が注入されることになるが、ソース及びドレイン領域となる高濃度不純物領域(n+領域)316の形成には特に支障は起こらない(図3(D))。

[0051]

また、LDD構造形成領域402に於いては、ゲート電極308を被覆しているレジストパターン315をマスクにイオン注入することにより、レジストパターン315から露出した領域に対応する多結晶シリコン膜302にソース及びドレイン領域となる高濃度不純物領域(n+領域)318が形成される。ゲート電極308の外側で且つレジストパターン315の内側の領域に対応する多結晶シリコン膜302には、既に第1のイオン注入処理により低濃度不純物領域(nー領域)319が形成されており、第2のイオン注入処理による高濃度不純物領域(n+領域)318の形成と合わせて、LDD構造多結晶シリコンTFTが構成される(図3(D))。

[0052]

また、シングルドレイン構造形成領域403に於いては、ゲート電極311か

1 6

ら露出した領域に対応する多結晶シリコン膜302に、既に第1のイオン注入処理により低濃度不純物領域(n-領域)314が形成されているが、その上に重なる様に第2のイオン注入処理により、高濃度不純物領域(n+領域)320が形成される。この様にシングルドレイン構造多結晶シリコンTFTは、ソース及びドレイン領域が高濃度不純物領域(n+領域)320のみで形成される構造になっている(図3(D))。

[0053]

尚、ここではGOLD構造及びLDD構造とシングルドレイン構造の多結晶シリコンTFTを別々に形成する方法について記載したが、光強度低減機能を有する補助パターンを設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105,110は、シリコン基板等の半導体基板を使用する同構造のMOS型トランジスタの形成にも、勿論適用可能である。この場合は、高濃度不純物領域(n+領域)及び低濃度不純物領域(n-領域)は、各々シリコン基板等の半導体基板に形成される。

[0054]

上記の実施形態1及び実施形態2で説明した本発明について、以下に記載する 実施例で更に詳細な説明を行うこととする。

[0055]

#### 【実施例】

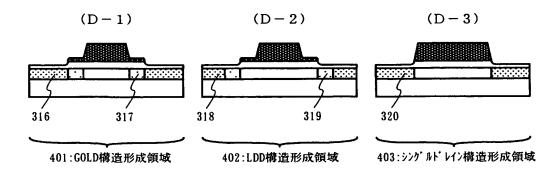

#### (実施例1)

回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクル101,105,110(図1(A),(B),(D))をゲート電極形成用のフォトリソグラフィ工程に適用し、GOLD構造及びLDD構造多結晶シリコンTFTで構成されるアクティブマトリクス型液晶ディスプレイの製造法について、図4~図8を用いて詳細に説明する。尚、実施形態2に於いては、GOLD構造とLDD構造及びシングルドレイン構造の多結晶シリコンTFTを別々に形成する方法について記載したが、本実施例に於いては、GOLD構造とLDD構造の多結晶シリコンTFTで構成される液晶ディスプレイの製造法について記載する。

[0056]

最初に、液晶ディスプレイ全体の回路構成を図4に示す。液晶ディスプレイは、画素領域501と画素領域501を駆動する為の周辺回路で構成されている。周辺回路は、シフトレジスタ回路502,506とレベルシフタ回路503,507とバッファ回路504,508とサンプリング回路505で構成されている。周辺回路であるシフトレジスタ回路502,506とレベルシフタ回路503,507とバッファ回路504,508には、ホットキャリア対策効果に優れたGOLD構造の多結晶シリコンTFTが使われており、一方、画素領域501と周辺回路の一部であるサンプリング回路505にはオフ電流値を抑える効果に優れたLDD構造の多結晶シリコンTFTが使われている(図4)。

[0057]

前記回路構成の液晶ディスプレイの製造法について、以下に図5~図8を用いて具体的に記載する。

[0058]

最初に、ガラス基板601上にプラズマCVD法により、各々組成比の異なる第1層目の酸化窒化シリコン膜602aを50nmと第2層目の酸化窒化シリコン膜602bを100nmの膜厚で堆積し、下地膜602を成膜する。尚、ここで用いるガラス基板601としては、石英ガラスまたはバリウムホウケイ酸ガラスまたはアルミノホウケイ酸ガラス等が有る。次に前記下地膜602(602aと602b)上にプラズマCVD法により、非晶質シリコン膜55nmを堆積した後、ニッケル含有溶液を非晶質シリコン膜上に保持させた。この非晶質シリコン膜を脱水素化処理(500℃−1時間)した後、熱結晶化(550℃−4時間)を行い、更にレーザーアニール処理により多結晶シリコン膜とした。次にフォトリソグラフィ工程及びエッチング工程により、この多結晶シリコン膜をパターニングし、半導体層603~607を形成した。この際、半導体層603~607を形成した後、TFTのVthを制御する為の不純物元素(ボロンまたはリン)のドーピングを実施しても構わない。次に半導体層603~607を覆う様に、プラズマCVD法により110nm厚の酸化窒化シリコン膜から成るゲート絶縁膜608を形成し、更にゲート絶縁膜608上に400nm厚のTaN膜から

成るゲート電極膜609をスパッタ法により堆積した(図5(A))。

[0059]

次に露光光の透過率を低減する機能を有するライン/スペースから成る回折格子パターンまたは半透膜で構成される補助パターンを設置したフォトマスクまたはレチクル101,105,110(図1(A),(B),(D))をゲート電極形成用のフォトリソグラフィ工程に適用し、両側が薄くなった形状のゲート電極形成用の現像後レジストパターン610a~615aを形成する(図5(B))。

[0060]

次にゲート電極形成用の前記現像後レジストパターン610a~615aをマスクに、TaN膜から成る400nm厚のゲート電極膜609のドライエッチング処理を行う。ドライエッチング後のゲート電極の形状は両側の端部が薄くなった凸型形状で、薄い領域の膜厚が初期膜厚400nmの5~30%程度(好ましくは7~8%程度、30nm程度)になる様にエッチングされ、ゲート電極617~622が形成される。この際、ドライエッチング工程に於けるレジストパターンの形状は、両側の端部のレジスト膜厚が薄く形成された現像後レジストパターンの形状は、両側の端部のレジスト膜厚の薄い領域が消失したドライエッチング後レジストパターン610a~615aから、レジスト膜厚の薄い領域が消失したドライエッチング後レジストパターン610b~615bの形状に変化している。また、ゲート電極617~622から露出した領域の酸化窒化シリコン膜から成るゲート絶縁膜608は、ドライエッチングにより薄くなった形状のゲート絶縁膜616に変化している。

[0061]

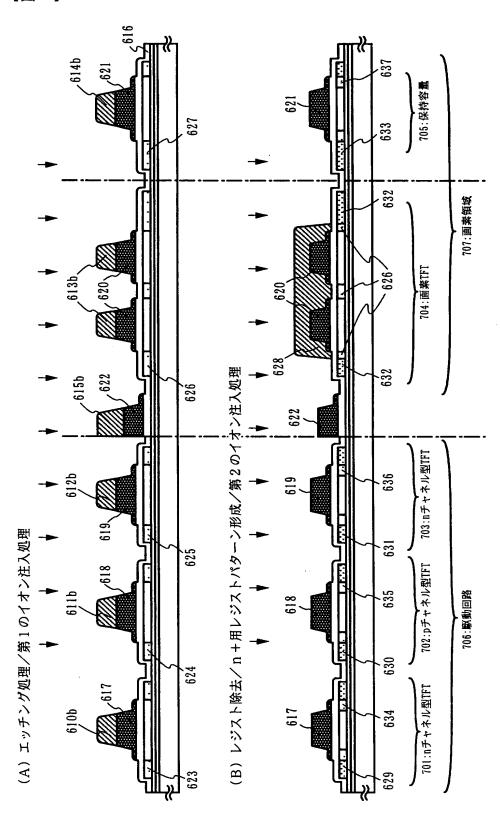

次にドライエッチング後レジストパターン610b~615bを除去せずに、第1のイオン注入処理である n型不純物の低濃度イオン注入を行い、ゲート電極617~622から露出した領域に対応する半導体層603~607に低濃度不純物領域(n 一領域)623~627を形成する。この際のイオン注入条件は n型不純物としてリン(nP)を用い、ドーズ量が3×10n2 ~3×10n3 atoms/c n2 及び加速電圧が60~100keVの条件で処理した(図6(A))。

[0062]

次に、ドライエッチング後レジストパターン610b~615bを除去する。 この後、画素TFT704をLDD構造にする為、当該領域に存在するゲート電極620を覆う様に、第2のイオン注入処理のマスクとなるレジストパターン628を形成する。

#### [0063]

そして、第2のイオン注入処理である n型不純物の高濃度イオン注入を行う。イオン注入条件としては、ドーズ量が $5\times10^{14}\sim5\times10^{15}$ atoms/cm $^2$ で、加速電圧が $60\sim100$  k e Vの条件でイオン注入する。

#### [0064]

この際、LDD構造形成領域の画素領域707である画素TFT704の領域に於いては、ゲート電極620を被覆しているレジストパターン628をマスクにイオン注入することにより、レジストパターン628から露出した領域に対応する半導体層606にソース及びドレイン領域となる高濃度不純物領域(n+領域)632が形成される。ゲート電極620の外側で且つレジストパターン628の内側の領域に対応する半導体層606には、既に第1のイオン注入処理により低濃度不純物領域(n-領域)626が形成されており、第2のイオン注入処理による高濃度不純物領域(n+領域)632の形成と合わせて、LDD構造多結晶シリコンTFTが形成される。

#### [0065]

一方、GOLD構造形成領域である周辺回路の駆動回路706に於いては、ゲート電極617~619をマスクにイオン注入が行われることにより、ゲート電極617~619から露出した領域に対応する半導体層603~605にソース及びドレイン領域となる高濃度不純物領域(n+領域)629~631が形成され、同時に当該ゲート電極617~619の両側に存在するゲート電極膜の薄くなった領域に対応する半導体層603~605に低濃度不純物領域(nー領域)634~636が形成される。この様に、ゲート電極617~619に於ける両側の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、高濃度不純物領域(n+領域)629~631と低濃度不純物領域(nー領域)634~636を同時に形成し、GOLD構造多結晶シリコンT

FTを形成することができる。

[0066]

尚、画素領域707の保持容量705に於いても、ゲート電極621(容量形成領域の為、正確にはゲート電極でなく単なる電極)をマスクに第2のイオン注入処理が行われる為、ゲート電極621の膜厚の違いを利用し、半導体層607に高濃度不純物領域(n+領域)633と低濃度不純物領域(n-領域)637が同時に形成され、構造的にはGOLD構造と類似の構造が形成されているが、多結晶シリコンTFTの形成領域でない為、GOLD構造ではない(図6(B))。

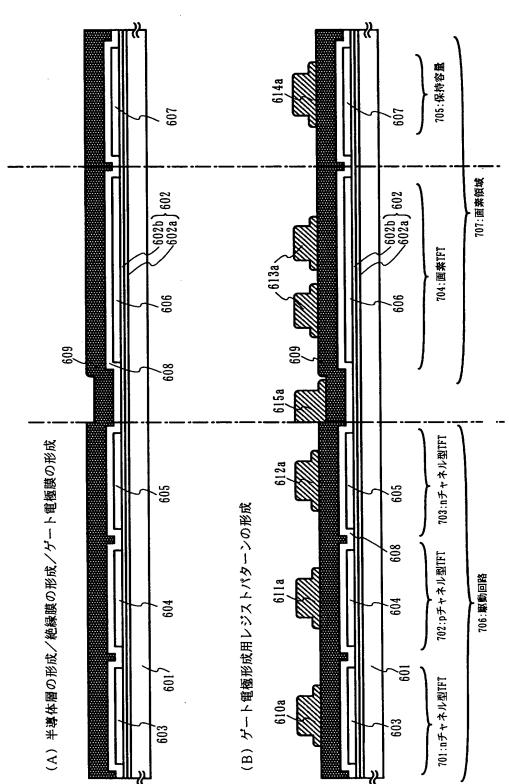

[0067]

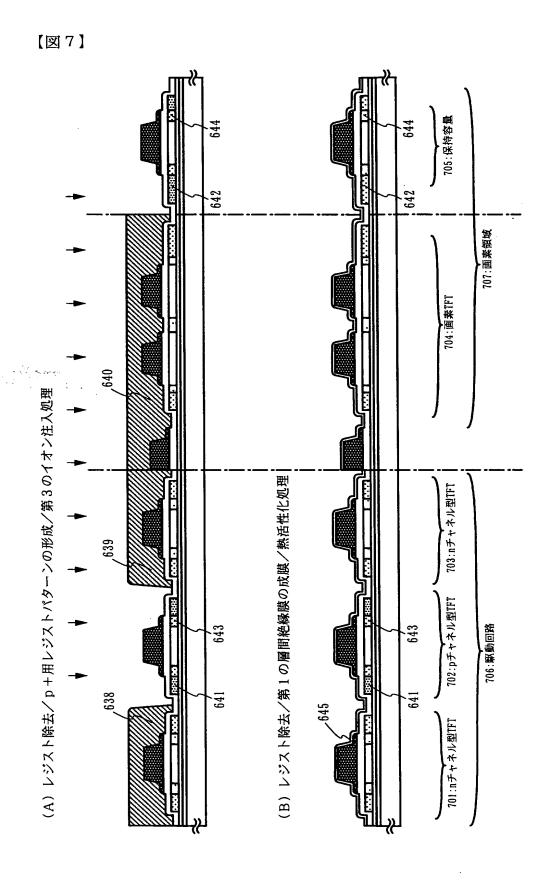

次に新規のフォトリソグラフィ工程を行うことにより、駆動回路706に於けるpチャネル型TFT702領域と画素領域707に於ける保持容量705領域をレジスト開口させ、その他の領域はレジストパターン638~640で被覆する様にパターニングする。

[0068]

前記レジストパターン638~640をマスクに第3のイオン注入処理である p型不純物の高濃度イオン注入を行う。この際、pチャネル型TFT702領域には、ゲート電極618をマスクに前記一導電型とは逆の導電型を付与する不純物元素であるボロン(B)等のp型不純物がイオン注入され、ゲート電極618から露出した領域に対応する半導体層604にソース及びドレイン領域となる高濃度不純物領域(p+領域)641とゲート電極618の両側の膜厚が薄い領域に対応する半導体層604に低濃度不純物領域(p-領域)643が形成され、GOLD構造多結晶シリコンTFTが形成される。第3のイオン注入領域は、第1及び第2のイオン注入によりn型不純物であるリン(P)が既にイオン注入されているが、p型不純物であるボロン(B)の濃度が2×10<sup>20</sup>~2×10<sup>21</sup>atoms/cm³となる様にイオン注入される為、pチャネル型多結晶シリコンTFTのソース及びドレイン領域として機能することができる。

[0069]

尚、保持容量705領域についても、pチャネル型TFT702と同様に、対

応する半導体層607に高濃度不純物領域(n+領域)642と低濃度不純物領域(n-領域)644が形成され、構造的にはGOLD構造と類似の構造が形成されているが、多結晶シリコンTFTの形成領域でない為、GOLD構造ではない(図7(A))。

### [0070]

次に前記レジストパターン638~640を除去した後、プラズマCVD法に より150nm厚の酸化窒化シリコン膜から成る第1の層間絶縁膜645を堆積 させる。更に、半導体層603~607に注入された各不純物元素を熱活性化処 理する為、550℃−4時間の熱アニール処理を行う。尚、本実施例では、TF Tのオフ電流値の低下及び電界効果移動度の向上の為、不純物元素の熱活性化処 理と同時に、半導体層603~607の結晶化の際に触媒として使用したニッケ ル(Ni)を高濃度のリン(P)を含む不純物領域629~633でゲッタリン グすることにより、チャネル形成領域となる半導体層中のニッケル(Ni)濃度 の低減を実現している。この様な方法で製造したチャネル形成領域を有する多結 晶シリコンTFTは、結晶性が良好で高い電界効果移動度を有する為、オフ電流 値の低下等の良好な電気特性を示すことができる。前記熱活性化処理は、第1の 層間絶縁膜645を堆積する前に行っても構わないが、ゲート電極617~62 2の配線材料の耐熱性が弱い場合には、本実施例の様に層間絶縁膜を堆積した後 に熱活性化処理を行う方が好ましい。次に、水素を3%含有する窒素雰囲気中で 4 1 0 ℃ - 1 時間の熱処理を行うことにより、半導体層 6 0 3 ~ 6 0 7 のダング リングボンドを終端させる為の水素化処理を行う(図7(B))。

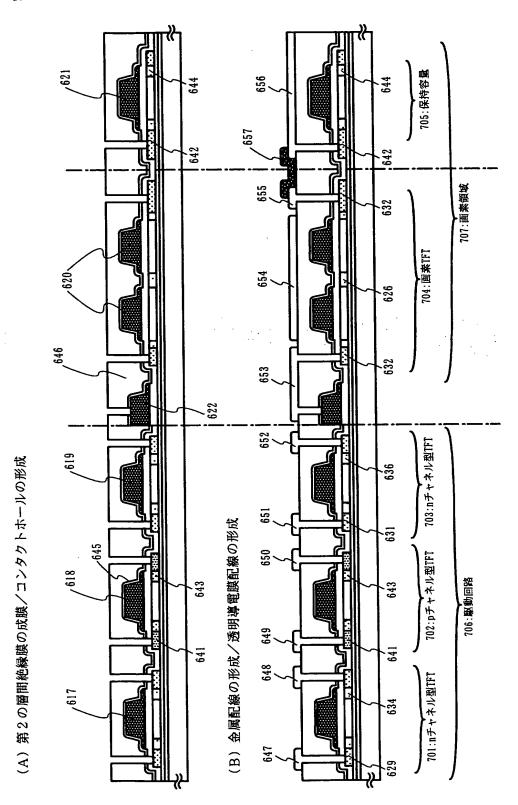

### [0071]

次に酸化窒化シリコン膜から成る第1の層間絶縁膜645上に1.6 $\mu$ m厚のアクリル樹脂膜から成る有機絶縁材料である第2の層間絶縁膜646を成膜する。その後、フォトリソグラフィ工程とドライエッチング工程により、ソース配線として機能するゲート電極622及び第1と第3のイオン注入領域である不純物領域629,631,632,641,642に接続する為のコンタクトホールを形成する(図8(A))。

[0072]

次に駆動回路706に於ける各不純物領域629、631、641と各々電気 的に接続する為の金属配線647~652を形成する。また画素部707に於け る接続電極653,655,656とゲート配線654を前記金属配線647~ 652と同時に形成する。尚、金属配線材料としては、50nm厚のTi膜と5 ○ ○ n m厚のA l - T i 合金膜の積層膜を適用している。接続電極 6 5 3 は、ソ ース配線として機能するゲート電極 6 2 2 と画素 T F T 7 0 4 とを不純物領域 6 32を介して電気的に接続する為のものである。接続電極655は画素TFT7 04の不純物領域632と電気的に接続しており、接続電極656は保持容量7 ○5の不純物領域642と電気的に接続している。ゲート配線654は、画素T FT704の複数のゲート電極620を電気的に接続する為のものである。次に 、ITO(Indium-Ti-Oxide)等の透明導電膜を80~120nmの厚さで堆積 し、フォトリソグラフィ工程とエッチング工程により、画素電極657を形成す る。画素電極657は、画素TFT704のドレイン領域である不純物領域63 2と接続電極655を介して電気的に接続され、更に保持容量705を形成する 一方の電極として機能する不純物領域642と接続電極656を介して電気的に 接続される(図8(B))。

[0073]

以上の様にして、nチャネル型TFT701、pチャネル型TFT702、nチャネル型TFT703を有する駆動回路706と、画素TFT704、保持容量705とを有する画素領域707で構成される液晶ディスプレイを製造することができる。

[0074]

#### (実施例2)

本発明は、様々な半導体表示装置(アクティブマトリクス型液晶表示装置、アクティブマトリクス型EL表示装置、アクティブマトリクス型EC表示装置)に適用することができる。従って、本発明は、前記半導体表示装置を表示媒体として組み込んだ電子機器全般に適用可能である。

[0075]

前記電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リ

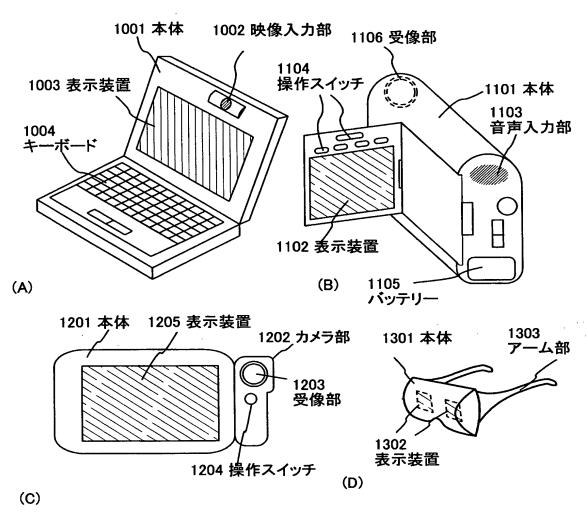

ア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、ゲーム機、カーナビゲーション、パーソナルコンピュータ、携帯情報端末 (モバイルコンピュータ,携帯電話または電子書籍等)等が挙げられる。それらの一例を図9~図11に示す。

[0076]

図9(A)はパーソナルコンピュータであり、本体1001、映像入力部1002、表示装置1003、キーボード1004で構成される。本発明を表示装置1003及び他の回路に適用することができる。

[0077]

図9 (B) はビデオカメラであり、本体1101、表示装置1102、音声入力部1103、操作スイッチ1104、バッテリー1105、受像部1106で構成される。本発明を表示装置1102及び他の回路に適用することができる。

[0078]

図9 (C) はモバイルコンピュータ (モービルコンピュータ) であり、本体1201、カメラ部1202、受像部1203、操作スイッチ1204、表示装置1205で構成される。本発明を表示装置1205及び他の回路に適用することができる。

[0079]

図9(D)はゴーグル型ディスプレイであり、本体1301、表示装置130 2、アーム部1303で構成される。本発明を表示装置1302及び他の回路に 適用することができる。

[0080]

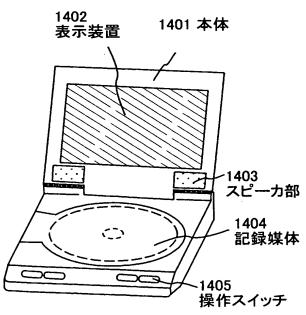

図9-Eはプログラムを記録した記録媒体(以下、記録媒体と略記)を用いるプレーヤーであり、本体1401、表示装置1402、スピーカー部1403、記録媒体1404、操作スイッチ1405で構成される。尚、この装置は記録媒体としてDVD、CD等を用い、音楽鑑賞またはゲームまたはインターネットを行うことができる。本発明を表示装置1402及び他の回路に適用することができる。

[0081]

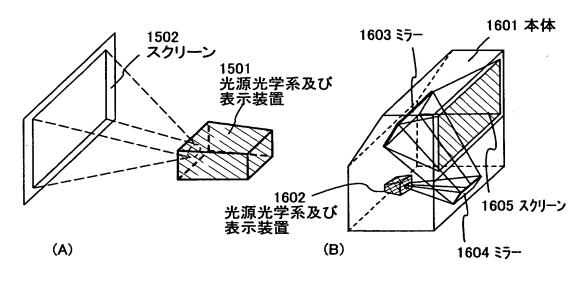

図10(A)はフロント型プロジェクターであり、光源光学系及び表示装置1501、スクリーン1502で構成される。本発明を表示装置1501及び他の回路に適用することができる。

[0082]

図10(B)はリア型プロジェクターであり、本体1601、光源光学系及び表示装置1602、ミラー1603、ミラー1604、スクリーン1605で構成される。本発明を表示装置1602及び他の回路に適用することができる。

[0083]

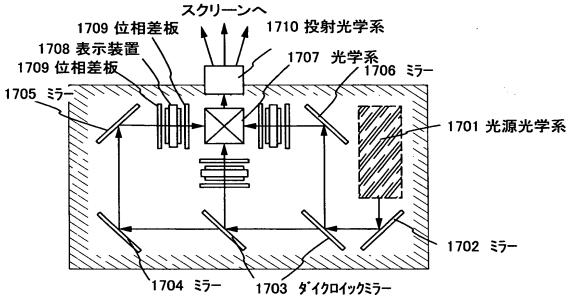

尚、図10(C)は、図10(A)及び図10(B)に於ける光源光学系及び表示装置1501、1602の構造の一例を示した図である。光源光学系及び表示装置1501、1602は、光源光学系1701、ミラー1702、1704~1706、ダイクロイックミラー1703、光学系1707、表示装置1708、位相差板1709、投射光学系1710で構成される。投射光学系1710は、投射レンズを備えた複数の光学レンズで構成される。この構成は、表示装置1708を3個使用している為、三板式と呼ばれている。また、図10(C)に於いて、矢印で示した光路に実施者が適宜、光学レンズ及び偏光機能を有するフィルム、位相差を調整する為のフィルム、IRフィルム等を設けても良い。

[0084]

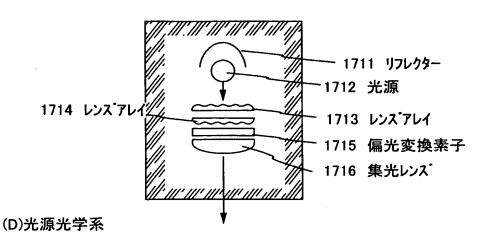

また、図10(D)は、図10(C)に於ける光源光学系1701の構造の一例を示した図である。本実施例では、光源光学系1701は、リフレクター1711、光源1712、レンズアレイ1713、1714、偏光変換素子1715、集光レンズ1716で構成される。尚、図10(D)に示した光源光学系は一例であり、この構成に限定されない。例えば、光源光学系に実施者が適宜、光学レンズ及び偏光機能を有するフィルム、位相差を調整するフィルム、IRフィルム等を設けても良い。

[0085]

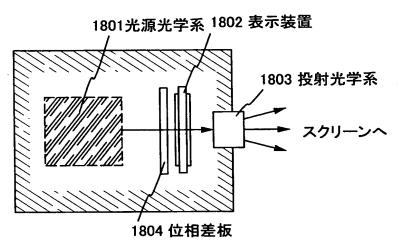

図10(C)は三板式の例を示したが、図11(A)は単板式の一例を示した図である。図11(A)に示した光源光学系及び表示装置は、光源光学系1801、表示装置1802、投射光学系1803、位相差板1804で構成される。

投射光学系1803は、投射レンズを備えた複数の光学レンズで構成される。図11(A)に示した光源光学系及び表示装置は図10(A)及び図10(B)に於ける光源光学系及び表示装置1501、1602に適用できる。また光源光学系1801は図10(D)に示した光源光学系を用いれば良い。尚、表示装置1802にはカラーフィルター(図示しない)が設けられており、表示映像をカラー化している。

[0086]

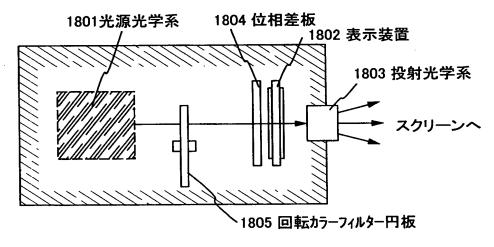

また、図11(B)に示した光源光学系及び表示装置は、図11(A)の応用例であり、カラーフィルターを設ける代わりに、RGBの回転カラーフィルター円板1805を用いて表示映像をカラー化している。図11(B)に示した光源光学系及び表示装置は図10(A)及び図10(B)に於ける光源光学系及び表示装置1501,1602に適用できる。

[0087]

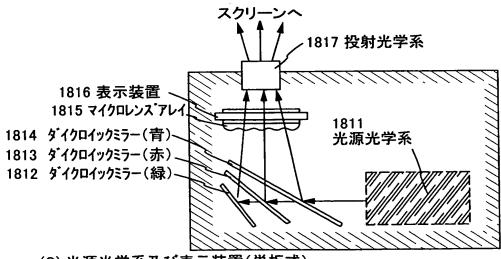

また、図11(C)に示した光源光学系及び表示装置は、カラーフィルターレス単板式と呼ばれている。この方式は、表示装置1816にマイクロレンズアレイ1815を設け、ダイクロイックミラー(緑)1812、ダイクロイックミラー(赤)1813、ダイクロイックミラー(青)1814を用いて表示映像をカラー化している。投射光学系1817は、投射レンズを備えた複数の光学レンズで構成される。図11(C)に示した光源光学系及び表示装置は図10(A)及び図10(B)に於ける光源光学系及び表示装置1501、1602に適用できる。また、光源光学系1811としては、光源の他に結合レンズ、コリメーターレンズを用いた光学系を用いれば良い。

[0088]

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。

[0089]

### 【発明の効果】

本発明は、マスクパターンに光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルをフォトリソグラフィ工程に適用

することにより、エッチング及びイオン注入工程を通し、簡単にGOLD構造トランジスタから成る半導体装置を製造可能とするものであり、半導体装置の性能向上と製造原価の低減に有効である。

#### [0090]

また、前記GOLD構造トランジスタの製造に於いては、マスクパターンに設置する光強度低減機能を有する補助パターンの寸法は任意の長さに設定可能である為、低濃度不純物領域(nー領域)のチャネル方向寸法も任意の長さに形成でき、GOLD構造トランジスタの性能向上に有効である。

#### [0091]

また、前記ゲート電極形成用フォトマスクまたはレチクルを利用した半導体装置の製造に於いて、イオン注入工程からのプロセスの変更により、オフ電流値の抑制効果の大きいLDD構造とホットキャリア対策効果の大きいGOLD構造トランジスタを回路毎に別々に形成可能である為、半導体装置の性能向上に有効である。

#### [0092]

また、前記ゲート電極形成用フォトマスクまたはレチクルを利用した半導体装置の製造に於いて、任意のマスクパターンに光強度低減機能を有する補助パターンを設置することにより、半導体装置の回路毎にシングルドレイン構造とGOL D構造及びLDD構造トランジスタを別々に形成可能である為、半導体装置の性能向上に有効である。

### 【図面の簡単な説明】

- 【図1】回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルのマスクパターン構成

- 【図2】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用したGOLD構造多結晶シリコンTFTの形成法【図3】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用したGOLD構造及びLDD構造とシングルドレイン構造多結晶シリコンTFTの回路毎形成法

- 【図4】液晶ディスプレイ全体の回路構成

- 【図 5】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用した液晶ディスプレイ製造法(1)

- 【図 6】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用した液晶ディスプレイ製造法(2)

- 【図7】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用した液晶ディスプレイ製造法(3)

- 【図8】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを利用した液晶ディスプレイ製造法(4)

- 【図9】半導体装置の一例を説明する図

- 【図10】プロジェクターの一例を説明する図

- 【図11】プロジェクターの一例を説明する図

#### 【符号の説明】

- 101:ゲート電極形成用フォトマスクまたはレチクル

- 102 : 遮光部

- 103 : スリット部(回折格子パターン)

- 104 : 透光部

- 105 : ゲート電極形成用フォトマスクまたはレチクル

- 106 : 遮光部

- 107 : スリット部 (回折格子パターン)

- 108 : 透光部

- 109 : 光強度分布

- 110:ゲート電極形成用フォトマスクまたはレチクル

- 111 : 遮光部

- 112 : 半透光部(半透膜)

- 113 : 透光部

- 114 : 光強度分布

- 201 : ガラス基板

202 : 多結晶シリコン膜

203a:ゲート絶縁膜(酸化窒化シリコン膜)

203b:ゲート絶縁膜(酸化窒化シリコン膜)

204a:ゲート電極膜

204b: ゲート電極

205a:現像後レジストパターン

205b:ドライエッチング後レジストパターン

206 : 高濃度不純物領域 (n+領域)

207 : 低濃度不純物領域 (n-領域)

301 : ガラス基板

302 : 多結晶シリコン膜

303:ゲート絶縁膜(酸化窒化シリコン膜)

304 : ゲート電極膜

305 :現像後レジストパターン

306 :現像後レジストパターン

307 : ドライエッチング後レジストパターン

308:ゲート電極

309:ゲート絶縁膜(酸化窒化シリコン膜)

310:ドライエッチング後レジストパターン

311:ゲート電極

312:ゲート絶縁膜(酸化窒化シリコン膜)

313 : 低濃度不純物領域 (n-領域)

314 : 低濃度不純物領域 (n-領域)

315 : レジストパターン

316 : 高濃度不純物領域 ( n + 領域)

317 : 低濃度不純物領域 (n-領域)

318 : 高濃度不純物領域 (n+領域)

319 : 低濃度不純物領域 (n-領域)

#### 特2000-244860

320: 高濃度不純物領域(n+領域)

401:GOLD構造形成領域

402 : L D D 構造形成領域

403:シングルドレイン構造形成領域

501 : 画素領域

502 : シフトレジスタ回路

503:レベルシフタ回路

504 : バッファ回路

505 : サンプリング回路

506:シフトレジスタ回路

507:レベルシフタ回路

508 : バッファ回路

601 : ガラス基板

602 : 下地膜

602a: 第1層目の酸化窒化シリコン膜

602b: 第2層目の酸化窒化シリコン膜

603 ~607 : 半導体層

608 : ゲート絶縁膜(酸化窒化シリコン膜)

609 : ゲート電極膜 (TaN膜)

610a~615a:現像後レジストパターン

610b~615b:ドライエッチング後レジストパターン

616 : ゲート絶縁膜

617 ~622 : ゲート電極

623 ~627 : 低濃度不純物領域 (n-領域)

628 : レジストパターン

629 ~633 : 高濃度不純物領域 (n+領域)

634 ~637 : 低濃度不純物領域 (n-領域)

638 ~640 : レジストパターン

641 ~642 : 高濃度不純物領域 (n+領域)

643 ~644 : 低濃度不純物領域 (n-領域)

645 : 第1の層間絶縁膜(酸化窒化シリコン膜)

646 : 第2の層間絶縁膜 (アクリル樹脂膜)

647 ~652 : 金属配線

653 :接続電極

654 : ゲート配線

655 ~656 :接続電極

657 : 画素電極 (ITO等)

701 : n チャネル型TFT

702 : p チャネル型TFT

703: nチャネル型TFT

704: 画素TFT

705 : 保持容量

706 : 駆動回路

707 : 画素領域

# 【書類名】

図面

【図1】

【図2】

# 【図3】

## (A) ゲート電極形成用レジストパターンの形成

# (B)ドライエッチング処理/第1のイオン注入処理

### (C) レジスト除去/LDD形成領域のレジストパターン形成

### (D) 第2のイオン注入処理/レジスト除去

# 【図4】

502:シフトレジスタ回路 (GOLD構造)

503:レベルシフタ回路 (GOLD構造)

504: バッファ回路 (GOLD構造)

505:サンプリング回路 (LDD構造)

506:シフトレジスタ回路 (GOLD構造) 507:レベルシフタ回路 (GOLD構造) 508:パッファ回路 (GOLD構造)

501:画素領域(LDD構造)

【図5】

【図6】

【図8】

# 【図9】

(E)

# 【図10】

## (C)光源光学系及び表示装置(三板式)

【図11】

(A)光源光学系及び表示装置(単板式)

### (B) 光源光学系及び表示装置(単板式)

(C) 光源光学系及び表示装置(単板式)

### 【書類名】 要約書

#### 【要約】

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる為、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する 補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程 を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

### 【選択図】 図1

# 出願人履歴情報

識別番号

[000153878]

1. 変更年月日 1990年 8月17日

[変更理由]

新規登録

住 所

神奈川県厚木市長谷398番地

氏 名

株式会社半導体エネルギー研究所